MIPS32 Architecture(Million instructions per second) is a RISC(Reduced Instruction Set Computer)based ISA(Instruction Set Architecture) has various features stated below:

- Simple Instructions with few number of addressing modes

- Large number of General Purpose registers(GPRs) and very few Special purpose registers

- Fixed length instruction which are easy to decode

- Simple Architecture for efficient pipelining

- Improved performance due to compiler scheduled pipelining

Instruction Set Classification:

MIPS32 instruction can be classified into the following functional groups:

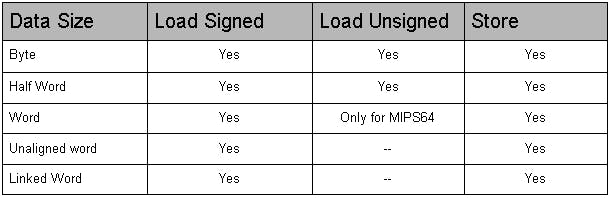

1.Load & Store Instructions:

MIPS32 is a Load-Store Architecture that is all operations are being performed on operands held in registers. Here, the main memory can only be accessed by load and store instructions.

There are various types of load and store instructions each of them are used for a particular purpose:

a). By specifying the size of the operand (w:word, H:half word, B:byte)

Eg.: LW(Load word), LH(Load Half word), LB(Load Byte), SW(Store word), etc.

b). By specifying whether the operand is signed(by default) or unsigned.

Eg.: LHU(Load half word unsigned), LBU(Load Byte unsigned), etc.

c). Accessing all fields that are not word aligned

Eg.: LWL(Load word left), SWL(Store word left), etc.

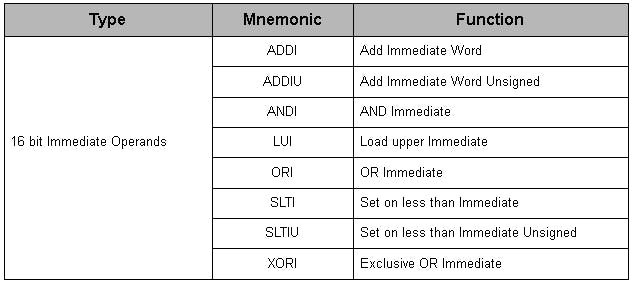

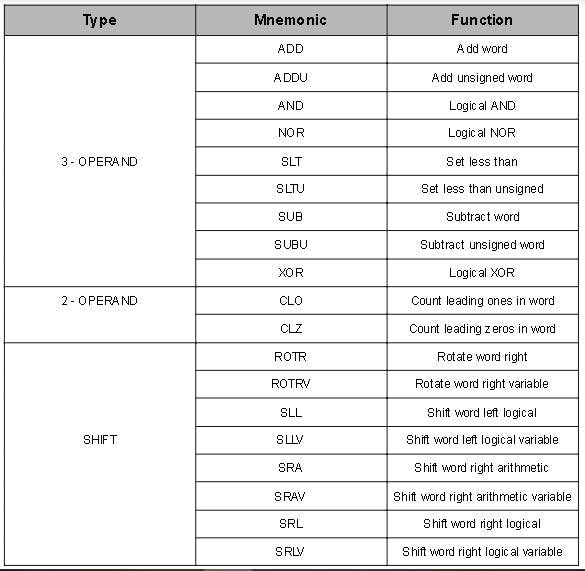

2.Arithmetic & Logic Instructions: All arithmetic & logic instructions operate on registers, it can be broadly classified into following categories:

- ALU immediate

- ALU 3-operand

- ALU 2-operand

- Shift

- Multiply & Divide

How it works?

How it works?

eg. SLTI $s1, $s2, 10

if $s1 < 10

then $s1 = 10

else $s1 = 0

More Instructions Under ALU

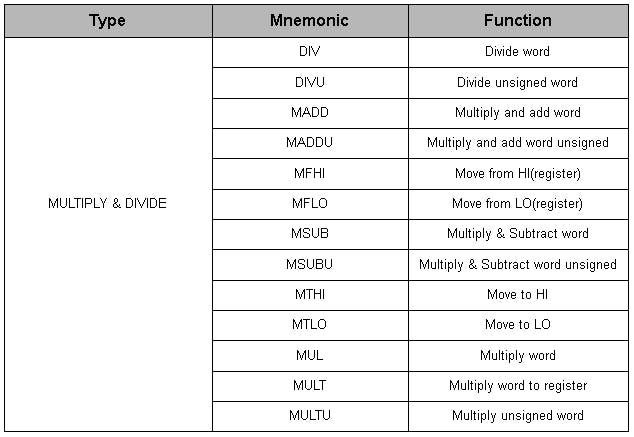

3.Multiply & Divide Instructions:

- The * & / instructions produce twice as many results bits, and are being stored in HI(high) and LO(low) registers pair:

- The multiplication results, the lower half of product is being stored in LO while the higher half in HI

- The divide operation results in a quotient that's being loaded LO and a remainder being loaded in HI

- Only exception is MUL instruction which delivers the result directly into the GPR(general purpose register)

Some Instructions set are as follows:

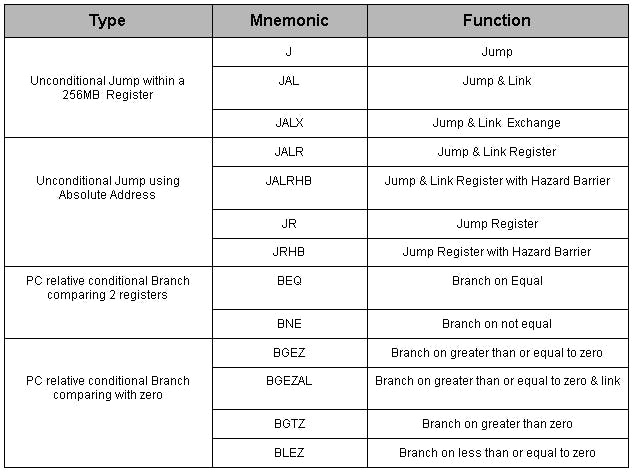

4.Jump & Branch Instructions:

The following types of Jump & Branch instructions are supported by MIPS32:

4.Jump & Branch Instructions:

The following types of Jump & Branch instructions are supported by MIPS32:

- PC(Program Counter) relative conditional branch, here an offset of 16-bit is added to PC

- PC region unconditional jump, here an offset is added to PC

- Absolute registers unconditional jump

- Special jump instructions that link the return address is R31

Some such Instructions are as follows:

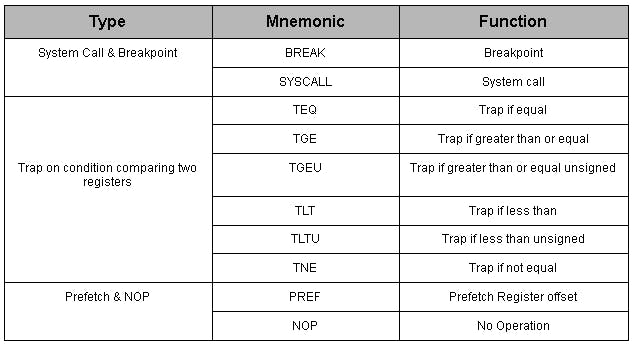

5.Miscellaneous Instruction: These instructions are used for various specific machine control purposes:

- It includes-

- Exception Instructions

- Conditional MOVE instruction

- Prefetch instructions

- NOP instructions

Some Instructions are follows:

6. Co-processor Instructions: The MIPS32 architecture defines four co-processor instructions as CP0, CP1, CP2, CP3.

- CP0 is also referred as system control co-processor as it handles the CPU chips, virtual memory system and exceptions

- CP1 is reserved for floating points

- CP2 is available for specific implementation

CP3 is available for future extensions

MIPS32 Instruction Encoding

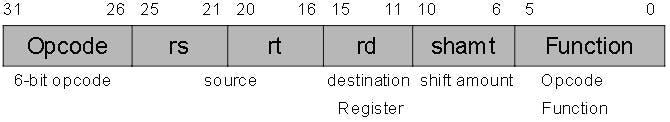

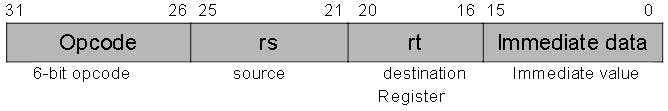

All MIPS32 instructions can be classified into three groups in terms of instruction encoding: R-type(Register), I-type(Immediate) and J-type(Jump Immediate).

- In an instruction encoding, the 32-bits of instruction are divided into several fields like source register, destination register and so on as per requirement.

- All instruction may not use all fields.

1.R-Type Encoding:

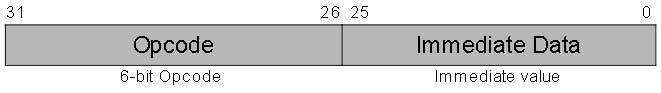

2.I-type Encoding:

2.I-type Encoding:

3.J-type Encoding:

3.J-type Encoding: